一级基础科目(一)辅导---触发器

9.3 触发器

数字电路中除了广泛采用门电路之外,还有一类基本单元电路,就是触发器。触发器有两个基本性质:(1)在一定的条件下,触发器维持在两种稳定状态(1或0状态)之一而保持不变;(2)在一定的外加信号作用下,触发器可以从一种稳定状态,转变到另一种稳定状态。这就使得触发器能记忆二进制信息1和0,被用作二进制存储单元。

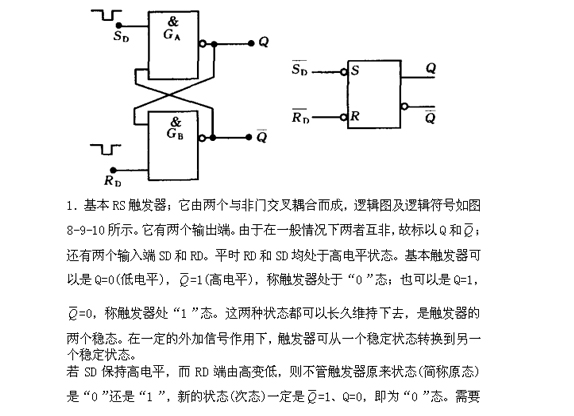

9.3.1 由与非门组成的基本触发器

说明的是,此后RD由低恢复为高,触发器仍能保持为“0”态。所以RD称置“0”输入端(也称复位端)。同理,若RD保持高电平、SD端送人负脉冲,则触发器一定置“1”状态。SD称置“1”输入端(也称置位端)。

如果RD和SD端同时由高变低,此时 和Q同时为1(称非定义状态)。此后若SD和RD同时回到高电平,则新状态既可能是“0”态,也可能是1态(称状态不定),取决于两个门延迟时间的不同。这种情况应当避免。

?08年考试规范、标准: 一级结构工程师 二级结构工程师

?2008年全国结构工程师各地考试报名信息汇总

?2009年一级结构工程师考试网上远程辅导招生简章!

?09年结构工程师老师辅导,现在报名可赠07、08年课程!

以上分析可用触发器功能表来表示,如表8-9―12。

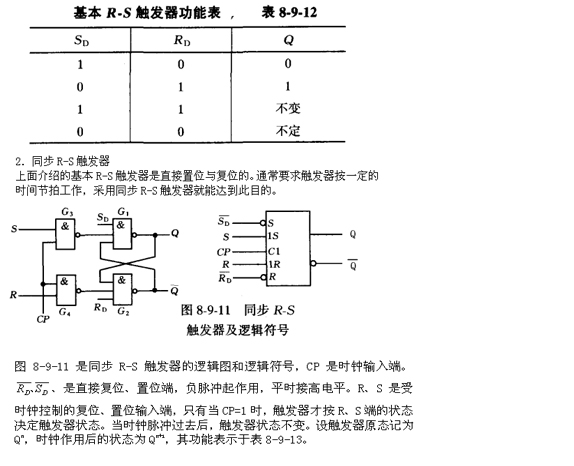

表中第一行说明当R=S=0时,时钟脉冲到来时(由0→1),触发器状态不变。

第二行说明当S端维持低电平,R端由0变1,当时钟脉冲到达后,触发器置0状态。第三行说明当R端维持为0,S端由0变1,当时钟脉冲到达后,触发器置1状态。第四行,当R,S都变1,时钟脉冲到达后。Q和 都为1。当时钟脉冲消失(由1变0)时,触发器状态不定,所以R=S=1的情况不允许存在。

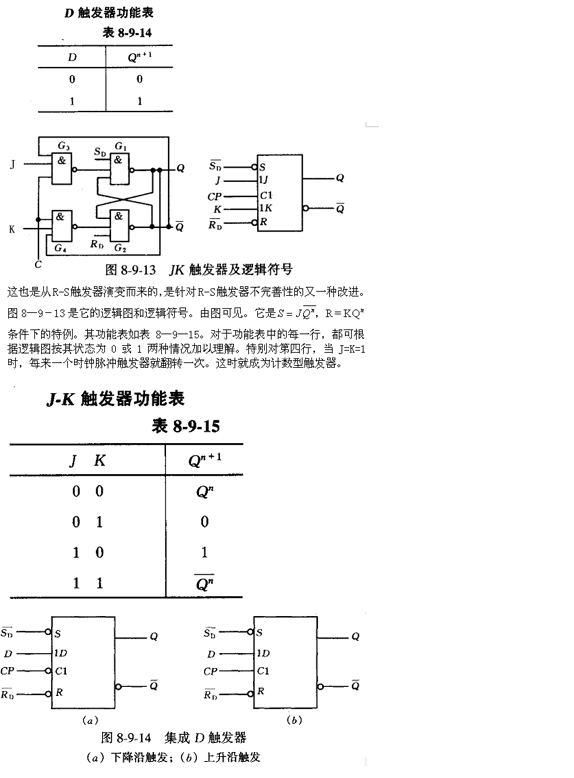

3.同步D触发器

同步R-S触发器存在着R=S=1时状态不定的问题,D触发器是针对这个问题的改进,它只有一个控制输人端D。图8-9-12是它的逻辑图和逻辑符号。由图可见,它是由R-S触发器演变而成的,是R= 条件下的特例。其功能表如表8-9―14由表可见,触发器在时钟脉冲作用后,新的状态Qn+1=D。

上述触发器,在时钟脉冲为高电平期间,若输入信号变化,输出状态随之变化。当它作为计数用时,就会出现空翻现象,没有实用价值,但作为理解触发器的功能来说它是很直观的。在实用的集成触发器中采用维持阻塞结构和主从结构的边沿触发器来解决空翻现,象。对其内部结构这里不作介绍。它的功能和逻辑符号与前述触发器一致,但应该明确,触发器根据输入控制信号的状态翻转是发生在时钟脉冲的上升沿或下降沿,其符号以集成D触发为例示于图8―9―14,其他集成触发器可类推。

最新资讯

- 环球网校双11预售开启!定金百倍膨胀,直播再返现金2023-10-25

- 环球网校结构工程师双11活动来啦,限时优惠!2023-10-25

- 注册结构工程师考试大纲下载2023-05-16

- 2023年一级注册结构工程师考试大纲内容2023-04-14

- 2023年结构工程师教材内容变动对比2023-04-10

- 2023年注册结构工程师专业基础教材变动对比2023-04-03

- 2023年新版注册结构工程师基础教材2023-03-29

- 2023一级结构工程师基础考试真题2023-01-29

- 2023年注册结构工程师专业考试大纲2023-01-06

- 2022年注册结构工程师 考试大纲2022-10-17

打卡人数

打卡人数